### SPECCTRAQuest Foundations

www.farsight.com.cn

# The SPECCTRAQuest Design Flow

The SPECCTRAQuest Design Flow consists of

the following six steps:

Pre-Placement

Solution Space Analysis

Constraint-Driven Floorplanning

Constraint-Driven Routing

Post-Route DRC

Post-Route Analysis

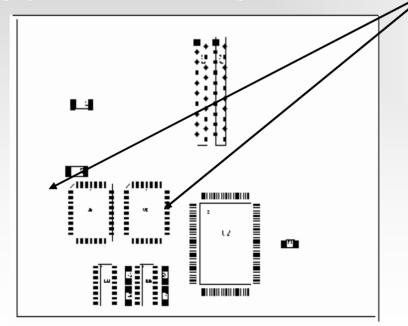

#### Design Flow: Pre-Placement

Standard form factors, mechanical restrictions, and standard practices often predefine locations of critical components.

Electrical design must start with these requirements, or present a strong case why things should be changed.

Pre-placed design is usually created by the CAD group as

a starting point for design.

Chip set placement

predetermined

#### Database Setup Advisor

- The first screen of the Database Seup Advisor.

- Explains the use of Database Setup Advisor.

- Ø Describes the steps you must take to set up the database correctly.

- Ø "Set up Right, Set up Once".

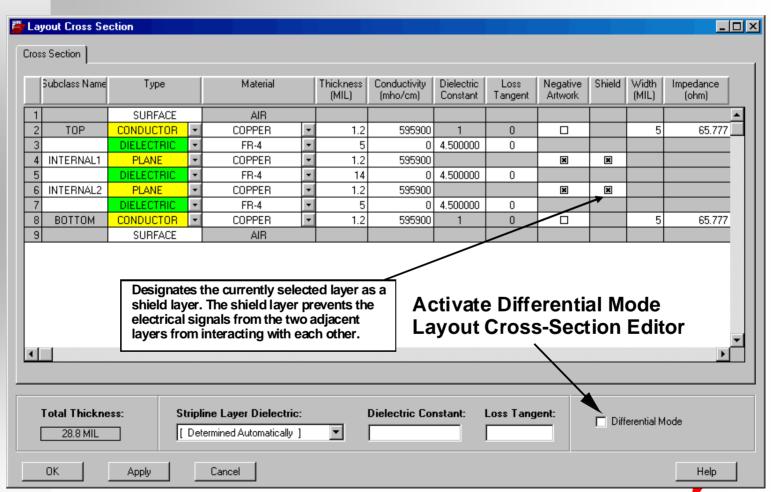

#### Defining the Layout Cross-Section

#### DC Voltages

SPECCTRAQuest SI Expert needs source voltages for terminators and capacitors to build an electrically correct circuit.

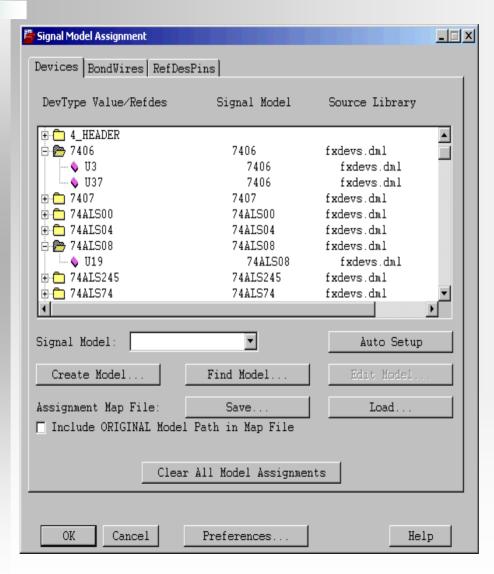

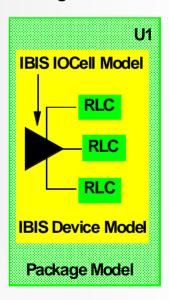

#### Signal Model

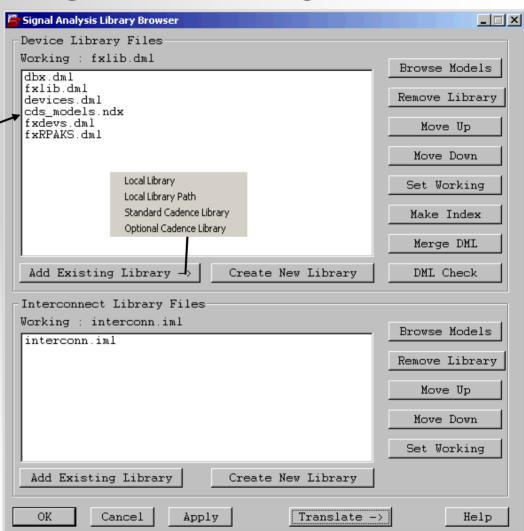

#### Translating and Adding Libraries

An Index file (.ndx) is a group of library files that have been merged and indexed together. You can use the models for simulation, but cannot modify the index file in any way.

You can translate these types of signal models to SPECCTRAQuest format.

#### **Pre-Route Template Extraction**

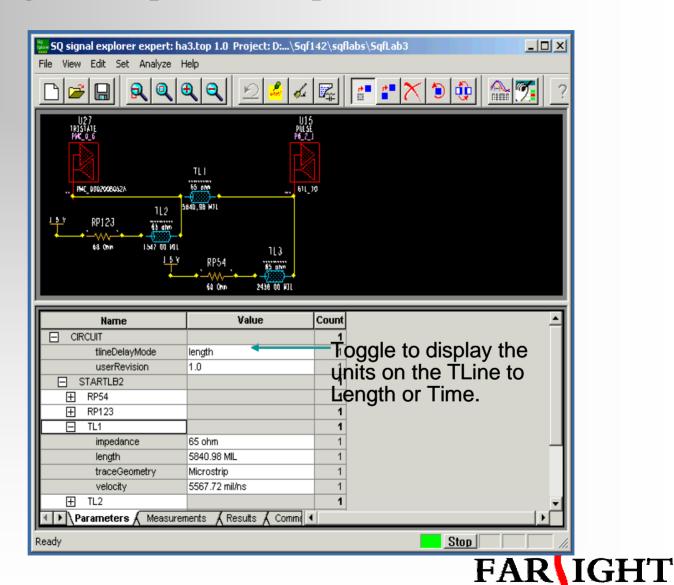

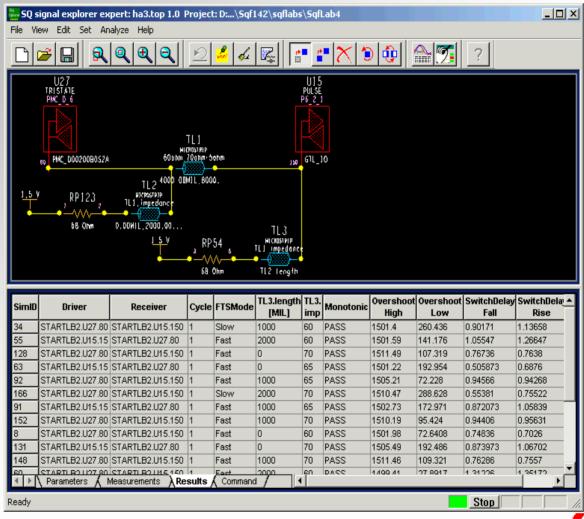

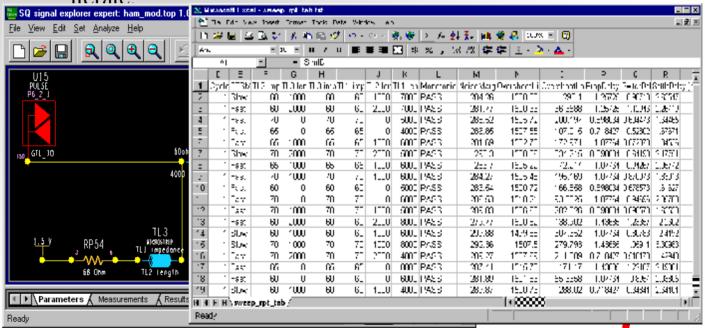

#### SQ Signal Explorer Expert Parameters Tab

#### SQ Signal Explorer Expert Results Tab

#### SigWave Current Waveforms \_ 🗆 × Untitled - SigWave Menu Bar **Tool Bar** .... ... ... ... ... ... ... ... ... B2 U15 150) STARTLB2 U15 150 Pulse Typ F ± ⊠ Views 🖮 📠 Waveform Libra case1 - Thu Nov 30 16:47:17 2000 Ė - 🔼 (STARTLB: ⊕ 🏂 Simulat ► M V\_CP1 20 Current [mA] 10 **W**aveform lib**ra**ry window window 20 10 30 Time [ns] V\_CP1 Status Bar Ready

FAR IGHT

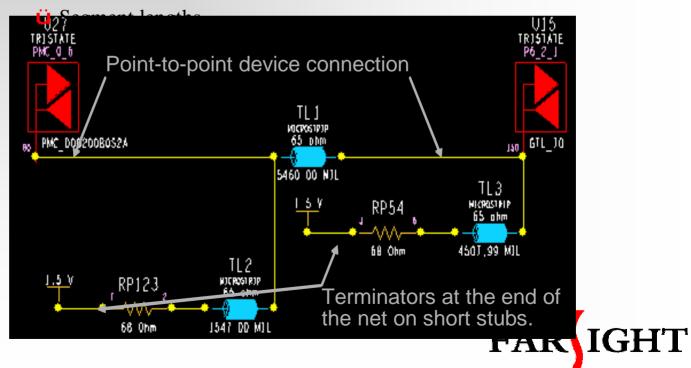

- **Ø** Extract / create topology to be analyzed.

- ü Pin ordering

- **ü** Discrete devices

- **ü** Rat-T positions (if any)

- Ø Identify / enter nominal values for all parameters.

- **ü** Board impedance

- **ü** Trace velocity

- **ü** Terminator value

- Identify manufacturing variances that are to be included in the analysis.

- **ü** Trace impedance (for example +/- 10%)

- **ü** Trace velocity

- **ü** Fast / slow components

- **ü** Device values (ex. terminators)

- **ü** Power supplies (if applicable)

- **o** Identify initial ranges for "design rule" parameters.

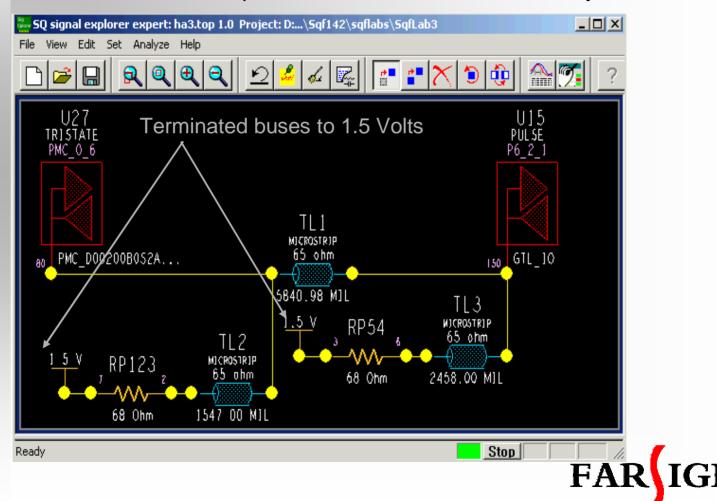

1.5 volt supply is +/- 5%

Trace impedance is 65 ohms +/- 5 ohms.

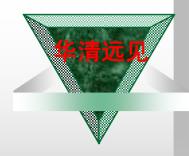

Trace length varies for each TLine: TL1: 4000 mils to 8000 mils, TL2 and TL3: 0 mils to 2000 mils.

FAR IGH

- Oreate a "master list" of all variables for analyses and their ranges.

- Identify "dependencies" between variables, based on how the design will be implemented.

**ü** Traces on the same layer have identical characteristics.

**ü** Resistors in the same RPAK match closely

|     |                    | OSCIV.                |              |               |              |         |       |

|-----|--------------------|-----------------------|--------------|---------------|--------------|---------|-------|

| CX. | $\mathbf{D}$       | Parameter<br>P6 Speed | Min          | Тур           | Max          | # Steps | 4 - 1 |

| O   | D                  | P6 Speed              | Fast         |               | Slow         | 2       | to be |

|     | an                 | 440FX_Speed           | Fast         |               | Slow         | 2       |       |

|     |                    | TL1 Impedance         | 60 ohms      |               | 70 ohms      | 2       |       |

|     |                    | TL1 Velocity          | 5400 mils/ns |               | 6600 mils/ns | 2       |       |

|     |                    | TL1 Length            | 4000 mils    |               | 8000 mils    | 2       |       |

|     |                    | TL2 Impedance         |              | TL1 Impedance |              | 1       |       |

|     |                    | TL2 Velocity          |              | TL1 Velocity  |              | 1       |       |

|     |                    | TL2 Length            | 0 mils       |               | 2000 mils    | 2       |       |

|     |                    | TL3 Impedance         |              | TL1 Impedance |              | 1       |       |

|     |                    | TL3 Velocity          |              | TL1 Velocity  |              | 1       |       |

|     |                    | TL3 Length            | 0 mils       |               | 2000 mils    | 2       |       |

|     |                    | RP A Impedance        | 67 ohms      |               | 69 ohms      | 2       |       |

|     |                    | RP B Impedance        | 67 ohms      |               | 69 ohms      | 2       |       |

|     | Total Combinations |                       |              |               |              | 512     |       |

- Ø Run simulations and gather results.

- USigXp "tabbed" report format is designed to import easily into Microsoft Excel and Access.

- Evaluate results and identify "cases" (combinations of variables) that cause topology to fail (not meet design goals).

- Simulate individual cases, analyze, correct design if needed, and iterate

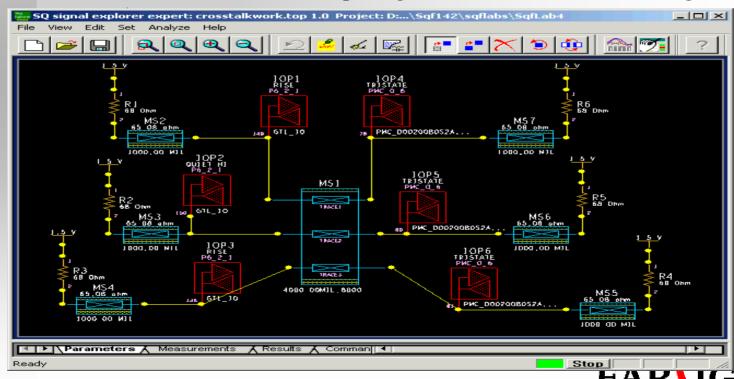

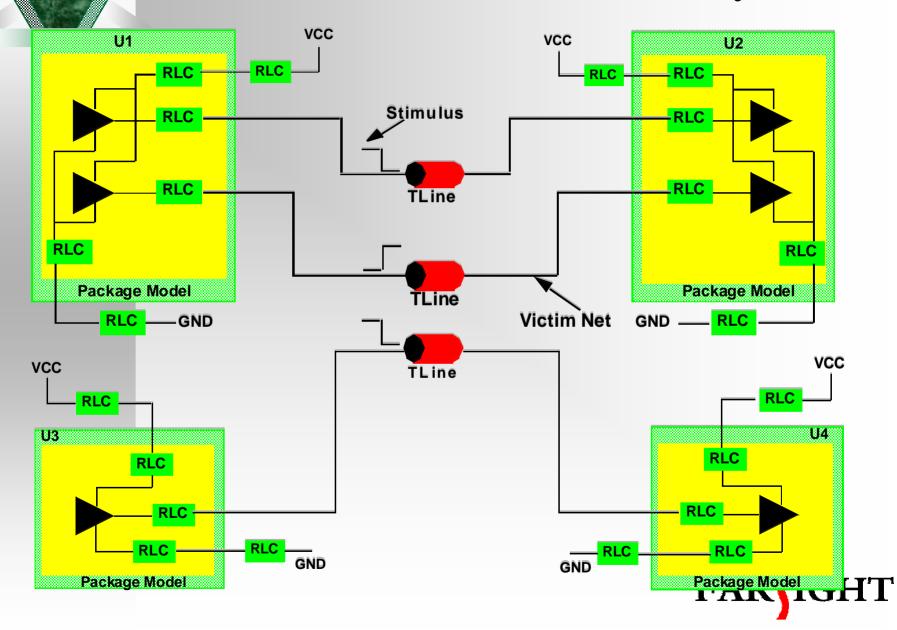

- **Ø** The solution found thus far is a single-line solution.

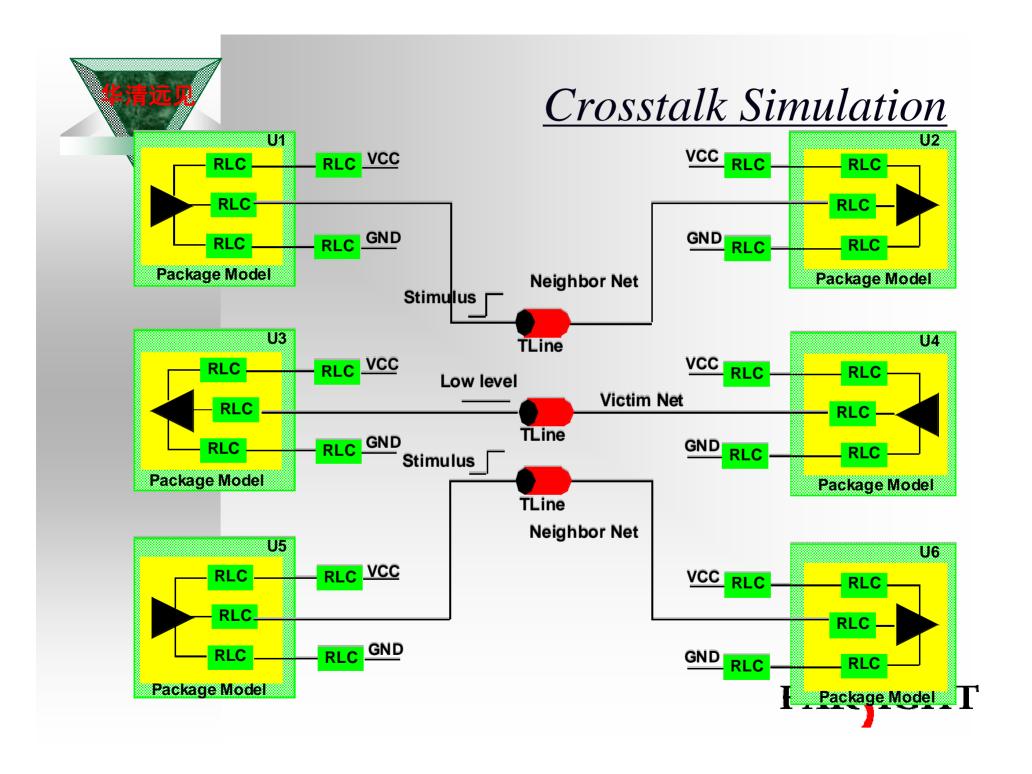

- Orosstalk timing shifts must be within crosstalk budget.

- Single-line topology is modified to model coupling where appropriate.

- **Ø** Different line width / spacing rules are evaluated for timing

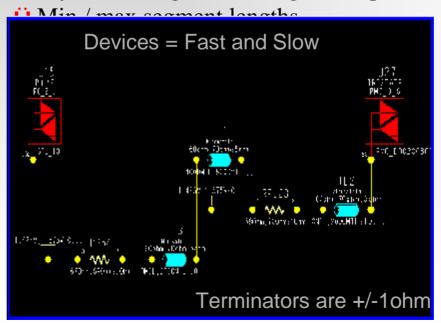

- **Ø** Create final topology template from analysis results:

- **ü** Segment min / max lengths

- ü Parallelism rules

- Some variances should not be included in the final topology template:

Terminators are +/-1ohm

FAR IGHT

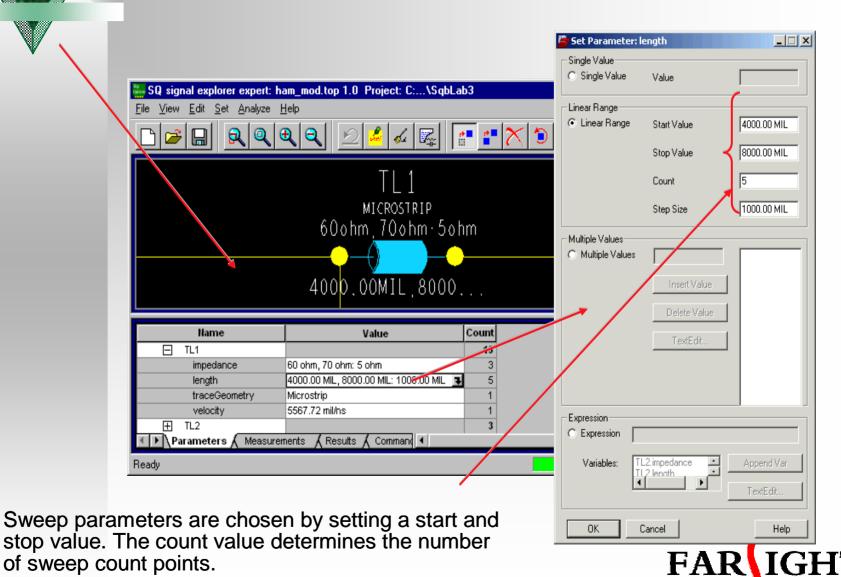

#### Setting Sweep Parameters

Count value determines the number of sweep count points.

Expression listed and other parameters used in the expression determine the number of sweep count points.

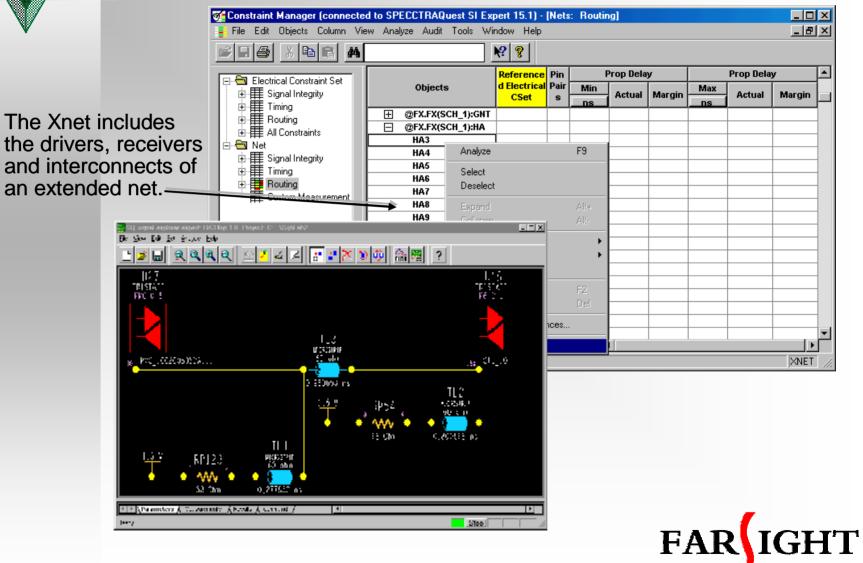

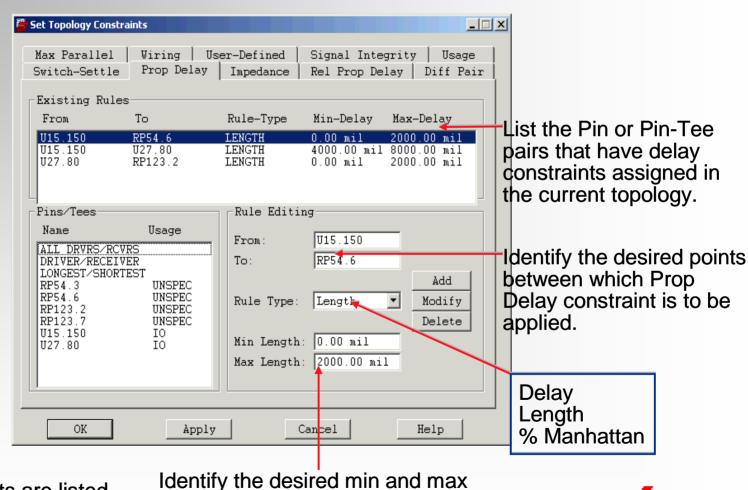

#### Assigning Prop Delay Constraints

Components are listed with their pinuse values.

Identify the desired min and max delay acceptable for this pair.

## Template Applications and Constraint-Driven Placement

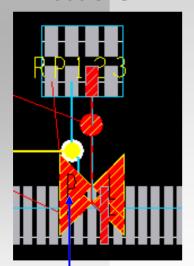

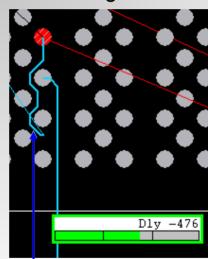

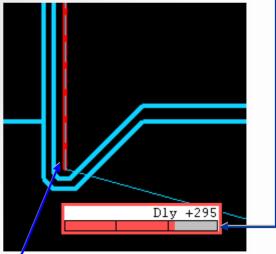

#### Constraint-Driven Routing

**Bubble: Off**

**Bubble: Hug Preferred**

The etch that is routed hugs the object to avoid DRC violation.

Dynamic timing meter highlights high-speed timing constraint violation.

**Bubble: Shove Preferred**

The etch that is routed pushes the existing etch to resolve DRC violation

The spacing rule violation flagged off by DRC markers

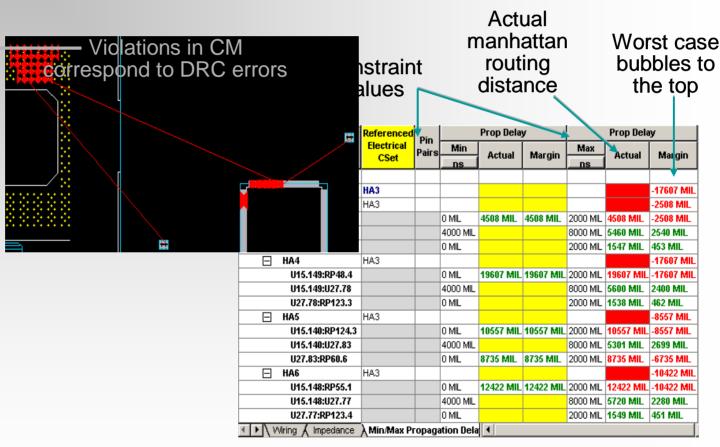

#### Post-Route DRC and Analysis

# Simultaneous Switching Ation: Noise Report

#### Results from a SSN simulation:

| Drvr                                                             | Net                                                | ******                                 | owerBus                                        |                            |                                    |                              |      | SSNFa           | 11 |

|------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|------------------------------------------------|----------------------------|------------------------------------|------------------------------|------|-----------------|----|

| COMPLETE U15 14                                                  | 9 COMPLETE                                         | НА4 рт                                 | wrgtl                                          | <br>0<br>                  | gn                                 | dbus                         |      | 51.54           |    |

| *******                                                          | ******                                             | *****                                  | ******                                         | ****                       | *****                              | *****                        | ***  | <del>(***</del> | ** |

| Driver I/O Char                                                  | acteristics                                        | (Typ F                                 | TSMode) R                                      | iseSle                     | ew/Fal                             | 1Slew :                      | in ( | mV/r            | s) |

| Drvr                                                             | IOModel                                            | Volmax                                 | Vohmin                                         | Rise                       | eSlew                              | FallS                        | lew  |                 |    |

| COMPLETE U15 14                                                  | 9 GTL_IO                                           | 400 mV                                 | 3000 mV                                        | 271                        |                                    | 284                          |      |                 |    |

| **************************************                           |                                                    |                                        |                                                |                            |                                    |                              |      |                 |    |

|                                                                  | teristics                                          |                                        |                                                |                            |                                    |                              |      |                 |    |

|                                                                  | teristics                                          |                                        | ******                                         | ****                       |                                    |                              |      |                 |    |

| Load I/O Charac                                                  | teristics<br>********<br>IOModel                   | ******                                 | *******<br>Vil                                 | *****<br>max '             | *****<br>Vihmin                    | *                            |      |                 |    |

| Load I/O Charac<br>**************<br>Rcvr<br><br>COMPLETE U27 78 | teristics<br>*********<br>IOModel<br><br>PMC_D0020 | ********<br><br>0B0S2AZZ               | *********<br>Vil<br><br>ZGHE 800               | *****<br>max '<br><br>mV : | ******<br>Vihmin<br><br>1200 m     | *<br>-<br>V                  |      |                 |    |

| Load I/O Charac<br>****************<br>Rovr                      | teristics<br>*********<br>IOModel<br>D0020         | ********<br><br>0B0S2AZZ               | *********<br>Vil<br><br>ZGHE 800               | *****<br>max '<br><br>mV : | ******<br>Vihmin<br><br>1200 m     | *<br>-<br>V                  |      |                 |    |

| Load I/O Charac<br>***********************************           | teristics<br>************************************  | ************************************** | *********<br>Vil<br>800<br>ZGHE 800<br>******* | ***** max ' my : *****     | *****<br>Vihmin<br>1200 m<br>***** | <br>*<br>-<br>V<br>-<br>**** |      |                 |    |

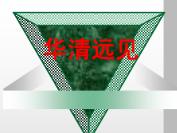

#### System-Level Analysis

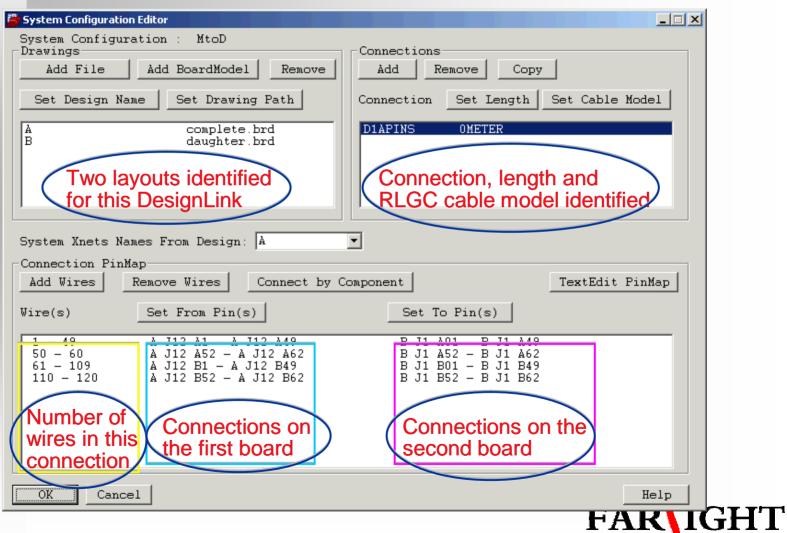

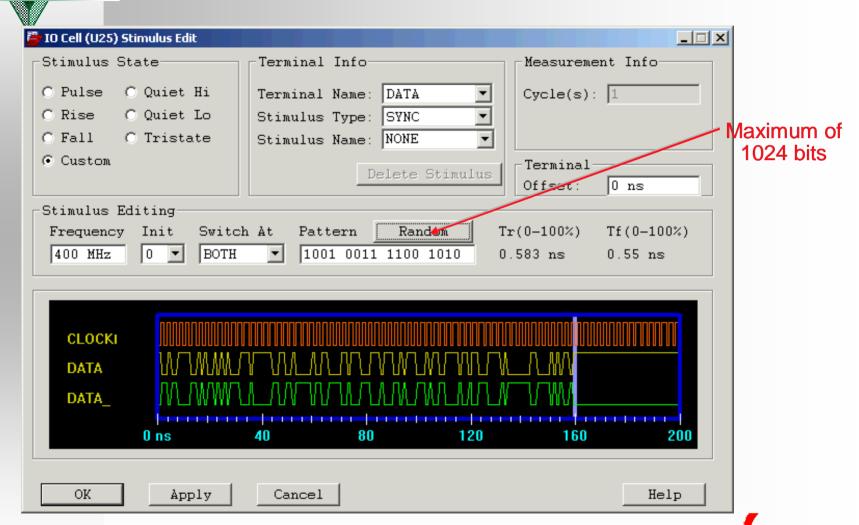

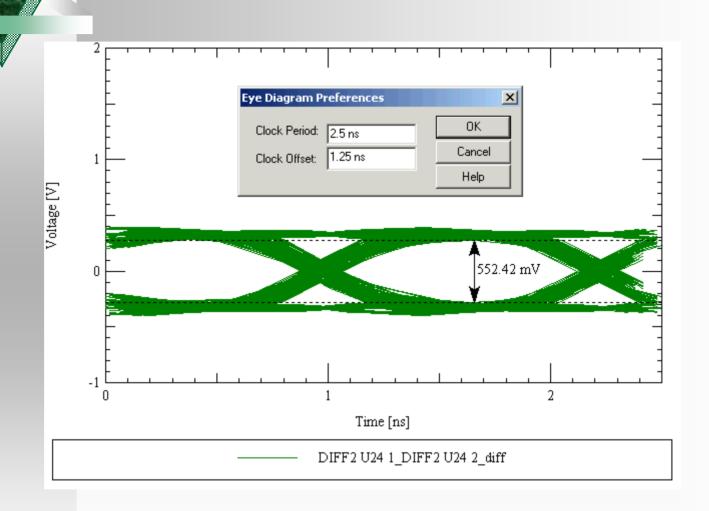

#### **Differential Pair Design Exploration**

## Custom Stimulus to Analyze Differential Pair Topology

#### Differential Pair Topology Analysis

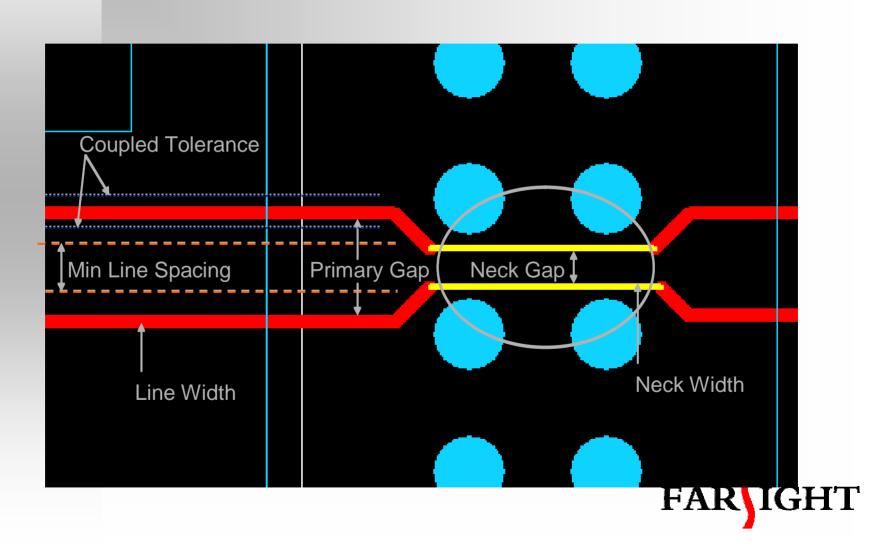

#### Gap and Line Width

From the SPECCTRAQuest SI Expert menu, select Route—Connect command.

### 华清远见CADENCE相关课程

- ∨ 勿级班(三天)

- ∨ 1. Concept HDL 原理图设计

- ∨ 2. Allegro PCB设计

- ∨ 3. Librarian Expert 库管理

- ∨ 高级班(三天)

- Day 1: Basic theories in high-speed PCB design

- Pre-Placement

- Extracting and Simulating Topologies

- V Day 2: Determining and Adding Constraints

- Template Applications and Constraint-Driven Placement

- ▼ Day 3: Constraint-Driven Routing

- Post-Route DRC and Analysis

- V Differential Pair Design Exploration

### 让我们一起讨论!

FAR IGHT

The success's road

www.farsight.com.cn

谢谢!