# FPGA系统设计的主要思路和方法初探

www.farsight.com.cn

# 今天的内容

- VFPGA的适用领域及选型

- VFPGA系统设计典型流程

- ∨FPGA逻辑设计方法—引入ASIC的设计方法

- VFPGA设计的常用技巧

- VFPGA系统设计中的对与错

# FPGA的适用领域及选型

### FPGA的适用领域

#### ∨应用领域

- Ø定制性功能, 批量不大 (大型<1ku, 小型<100ku)

- ◎需变化功能(标准变化,指标变化)

- Ø连接及接口功能 (bridge or glue logic)

- ∅产品差异化, 专利实现

- ØASIC 原型验证

### FPGA的选型

#### V厂商选择

- ØAltera(亚太使用第一)

- ØXilinx (欧洲使用第一)

- ØLattice (边缘市场)

- ØActel (字航应用第一)

- Ø其他 (growing) 建议使用Altera或Xilinx产品,占整个市

90%, 性价比高, 软件成熟

### Altera & Xilinx

Altera Xilinx

共同特点:系列化和应用专门化

### Altera 器件选择

- ∨高端: Stratix系列, 目前主流 StratixII/StratixIII

- ∨低成本: Cyclone系列, 目前主流 Cyclone2/3系列, 大多数消费类, 通 讯类应用已经足够, 成本是stratix系 列1/5~1/10

- V需要高速串行连接采用Stratix下的 GX系列, Arria系列兼顾低成本和 串行连接, 但灵活性和速度有限制

FAR IGHT

### 器件选择原则

- V"喜新厌旧": 性能高, 功耗低, 价格低, 支持标准多

- V不求大而全, 够用就好

- ✓速度等级尽量选用最低的:成本考 虑

- V留有余量。可升级考虑

- Ⅴ环保要求注意考虑无铅型号

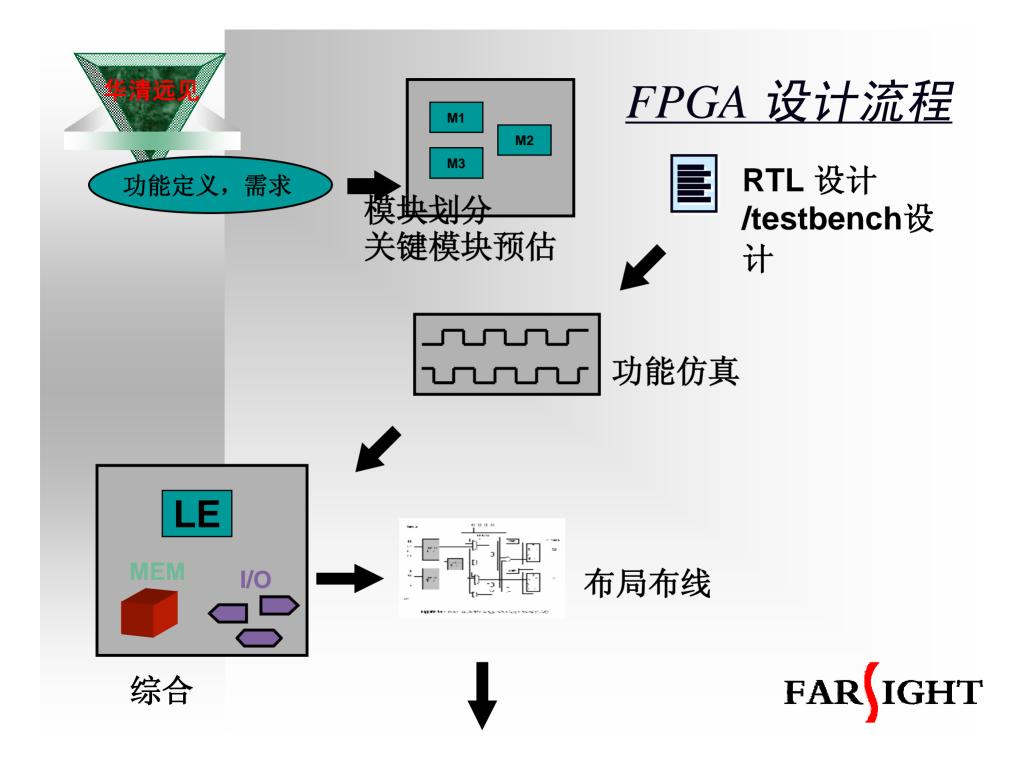

### FPGA系统设计典型流程

### VFPGA系统设计两方面:

- (1) FPGA逻辑功能设计

- (2) FPGA器件板极集成设计

两者必须综合考虑, 管脚分配, 时钟分配, IO标准, 同步方式, 总线宽度等. 都会与逻辑实现相互影响

### 时序分析

性能是否满足要求, 关健路径分析

#### 后仿真

将器件参数,实际延迟,扇出考虑到设计中的仿真

#### 板级调试

### 以设计一个FPGA视频解码为例

- (1) 功能定义,需求分析:主要考虑 采用哪些设计技术和接口,以决定 信号频率,格式,解压比,是否外 挂存储器.输入输出带宽等

- (2) 模块划分, 关键模块估计: 将设计思路清晰化, 大型FPGA设计的最重要阶段, 注意层次化。前端信号捕捉整序模块, 运动估计模块, 路径主控模块, DDR SDRAM控制模块, HDMI输出模块等

(3) RTL/testbench代码编写:实现阶 段. 注意严格按照模块定义. 先分 析本模块内的状态机/异常处理/接口 再写代码,例如视频通路的控制模 块. 输入事件与控制输出的状态机 一定要清楚, 可能的FIFO溢出。视 频失锁等一定要作好保护, 本级的 寄存器级数要心中有数。

- ∨功能仿真:建议采用第三方仿真工具, PC领域最常见的是modelsim,注意使用 FPGA厂商提供的库

- ∨综合:可以采用第三方的软件,如synpify, Precision等,也可以使用Quartus或ISE自 带的综合器,注意加入约束

- ∨ 布局布线: 只能使用FPGA厂商工具

- ∨时序分析:看时序分析报告是否满足约束,察看关键路径,看是否有可优化的地方.如不满足时序要求需回归设计

FAR IGHT

- V后方真:将反标的物理信息带入的方真, 仿真速度慢很多, 对大型设计有仿真时间可行性问题

- ∨板极调试:将文件下载到FPGA板级 调试,注意下载方式与生成文件的 对应。

## FPGA逻辑设计方法—引入ASIC 的设计方法

- VASIC领域的一些可借鉴方法

- (1) 静态时序分析代替大部分后仿真

- (2) 设计有利于IP复用的模块

- (3) 增量编译,逻辑锁定

- (4) SOC软硬件联合设计

. . . . . .

V静态时序分析代替大部分后仿真 FPGA设计规模已经达到数百万广 级. 完全后仿需要数天时间. ASIC 普遍采用功能仿真+静态时序分析+ 关键模块时序仿真的方法。对FPGA 设计如果设计报告余量足够. 一般 可以在前仿充分, 约束设置合理的 前提下不进行后仿

#### V设计有利于IP复用的模块

ASIC领域的IP复用已经成为必须, FPGA设计利用成熟的IP可以大大加快设计,在自己设计时尽量设计接口清晰标准,以功能划分模块,设计模块在不影响性能的前提下尽量采用寄存器输入输出,逐渐积累自己的功能模块和仿真模块。

#### V增量编译、逻辑锁定

FPGA工具逐渐推出增量编译,这来源于ASIC的模块down-top编译,逻辑锁定来源于ASIC设计中的模块布局布线锁定。前者可以大大加速大型FPGA设计的编译,后者可以更好的实现时序收敛

#### VSOC软硬件联合设计

ASIC领域的SOC设计为逻辑设计引入CPU及软件,实现更灵活的设计,FPGA采用嵌入的CPU核也可以达到同样的效果,已经有很多成熟的CPU内核可供使用。注意软硬件的联合设计,利用好FPGA厂商提供的SOPC工具。

# FPGA设计的常用技巧

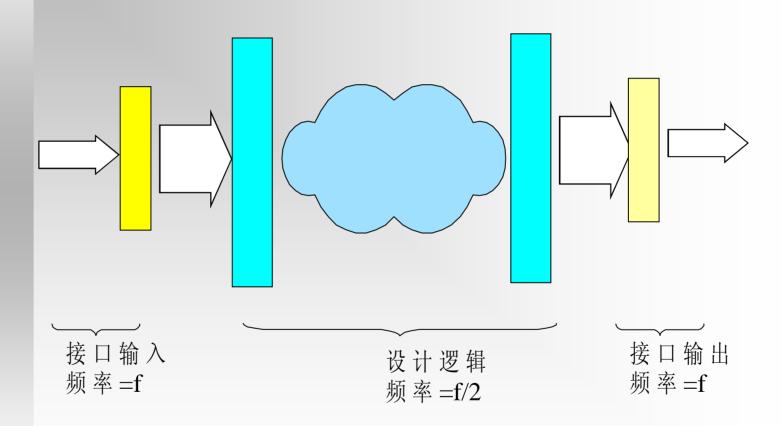

- ∅串并转换

- ∅乒乓操作

- ◎流水线操作

- ∅查表操作

- Ø PLL移相

- Ø .....

#### 串并转换

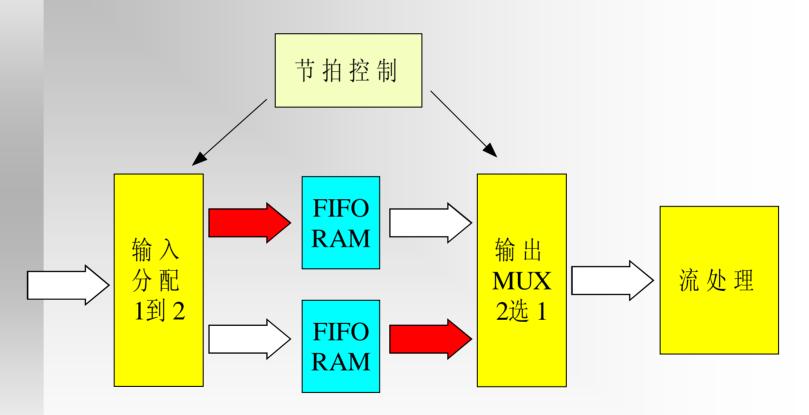

### 乒乓操作

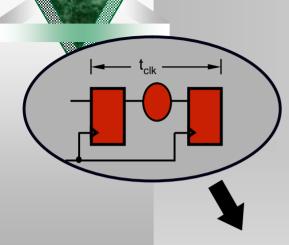

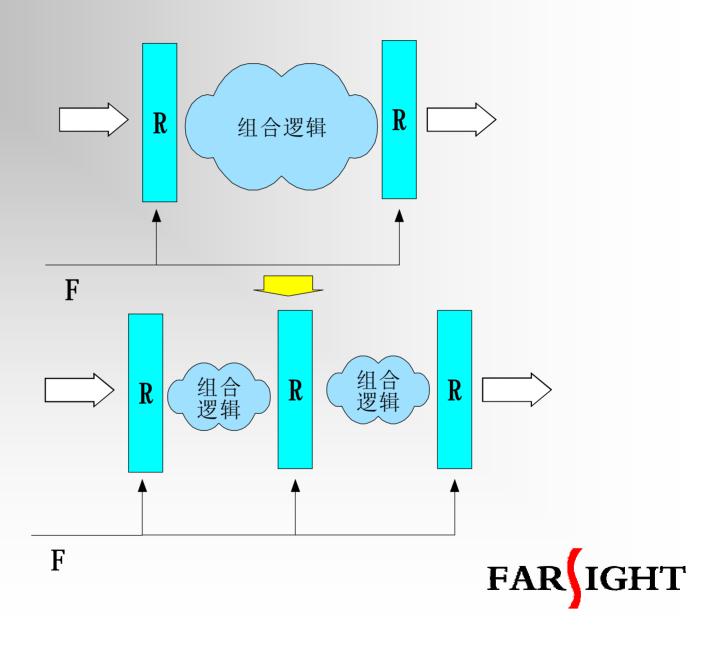

#### 流水线操作

∨对某些数据变换操作,如编解码, 输入输出组合有限,当算法的实现 非常复杂时,采用将输入输出关系 表颁存于RAM中的方式,利用查表 直接得出结果

### PLL移相

▼利用FPGA內部的PLL/DLL,在源同步系统中将工作钟和输出钟进行移相(一般180度),可以使下游输入程等是够的输入建立时间,便于数据采样

### FPGA系统设计中的对与错

- VX:这个模块太简单不用仿,直接 上板子调

- ✓正:任何模块都要经过仿真调试, 且要注意仿真的覆盖率

- 注:不要因为FPGA可以改就只重视调 不在乎仿真,要养成没仿真的设计 不上板子的好习惯

- VX: 武断认为某款FPGA太慢, 一综 合不行就换器件

- V正:查找关键路径,优先采用代码级的速度优化技术,其次采用综合优化技术。

- 注:绝大多数的FPGA设计都可以通过 代码和综合技术的优化提高性能

VX: 仿真就是看波形

✓正:波形结合条件输出和断言分析

注:复杂的设计在仿真时可以采用打印输出和条件判断输出以及断言告警的方法来输出仿真结果,甚至可以通过良好的仿真模型和检查模块实现自动检查。

VX:把FPGA资源过度充分利用,比如用99%的资源

✓正: 留有一定的资源余量

注:FPGA器件在资源实用非常高时会导致时序性能的急剧下降,一般一个产品设计时FPGA的资源利用率最分不要超过80%,同时兼顾管脚兼容性升级

# 让我们一起讨论!

嵌入式培训专家

### FAR IGHT

企业文化: 诚信、创新、开放、合作

FAR IGHT

The success's road

www.farsight.com.cn

谢谢!