# Cortex-M3体系结构与接口编程

# 今天的内容

- ØCortex-M3发展及应用

- ØCortex-M3内核体系结构

- ØThumb2指令集

- ØCortex-M3接口设计

- ØCortex-M3与操作系统

## Cortext-M3 发展及应用

#### VARM公司简介

- Ø主要设计ARM系列RISC处理器内核(芯片的体系结构设计与开发)

- ❷授权ARM内核给生产和销售半导体的合作伙伴, ARM 公司不生产芯片

#### VARM系列的内核简介

Ø到目前为止,ARM公司设计的内核如下图所示

## ARM公司目前设计的内核

Halfword and signed halfword / byte support

System mode

Thumb instruction set

Improved ARM/Thumb Interworking

CLZ

Saturated arithmetic

DSP multiplyaccumulate instructions

Extensions:

Jazelle (5TEJ)

SIMD Instructions

Multi-processing

V6 Memory architecture

Unaligned data support

Extensions:

Thumb-2 (6T2)

TrustZone (6Z)

Thumb-2

CoreSight

7A (Applications)

NEON

7R (Real-time)

Hardware divide

7M (Microcontroller)

Thumb-2 ONLY

## The Architecture Challenge

XScale 英特尔公司的一款产品

ARM核被广泛的采用: 2004年基于ARMv4T & ARMv5T架构 的内核(ARM7TM, ARM9TM, ARM10TM 和 XScaleTM 处理器家族)出货量 > 1200万 个

ARMv6架构的内核也越来越多的被 采用(ARM11™ processor family)

New demands and usage diversity continue

**ARMv7:** Satisfying diverse markets while maintaining consistency is key:

Architecture profiles

#### *Meeting the challenge with profiles (1/2)*

- **∨** The Application profile (ARMv7A)

- Ø内存管理单元支持 (MMU)

- ❷在低功耗上具有高效的性能

**ü**Influenced by multi-tasking OS system requirements

- TrustZone and Jazelle-RCT for a safe, extensible system

- Øe.g. Cortex-A8

- ▼ The Real-time profile (ARMv7R)

- **Ø** Protected memory (MPU)

- **O** Low latency and predictability 'real-time' needs

- **Ø** Evolutionary path for traditional embedded business

- Øe.g. Cortex-R4

#### *Meeting the challenge with profiles*(2/2)

- ▼ The Microcontroller profile (ARMv7M)

- Lowest gate count entry point

- **Ø** Deterministic behavior a key priority

- Øe.g. Cortex-M3

## Cortex-M3市场定位

- ∨ Cortex-M3是ARM公司定位于与8、16位MCU竞争的芯片。

- ▼ Cortex-M3更适合MCU这样的应用,因为MCU 并不需要大量的计算。ARM7设计出来与传统的 MCU不同,性能达50MHz,甚至需要uC/DOS、 Linux这样的操作系统,计算特点较强。而 Cortex-M3功能更加灵活,更像MCU,例如你 什么功能不用就关闭掉,指令集等都经过优化

- ∨ST, NXP

## <u>今天的内容</u>

- ØCortex-M3发展及应用

- ØCortex-M3内核体系结构

- ØThumb2指令集

- ØCortex-M3接口设计

- ØCortex-M3与操作系统

#### ARM Cortex-M3 Processor Macrocell **Debug and Sleep** 3-Stage Pipeline, Harvard Architecture, Non Maskable Control Thumb-2 ISA (or Thumb) 30K\* Gates Interrupt **Optional** 1-240 Configurable Configurable **ETM** ARM. **Interrupts** nested VIC **Configurable Priority** ARM core Levels Serial Wire Memory DAP SWD or JTAG protection unit Viewer Flash Patch & **Breakpoints** Data Flash 2 watchpoints patch 0 **Bus Matrix Data Watchpoints** & Trace Flash SRAM peripheral I/F interface Cortex M3 Total \* Preliminary gate counts & power consumption based on initial implementation 60k\* Gates Gate Counts are based on TSMC 0.18 at 50MHz Optional ETM & MPU gate counts not included

#### ARM Cortex-M3 32-bit 微控制器

- ∨ 基于Thumb-2 的处理器内核 (具有完整的 Thumb 兼容性) Ø 具有16位和32位混合指令编排的高代码密度

- ∨ 16个32位寄存器

- V 卓越的编译器

- ✓ 減少引牌需求

- V 高效的中断处理

- V 电源管理

- V 乘法/除法指令

- ✓ 高效率的调试和发展支持特点

- Ø Breakpoints, Watchpoints, Flash Patch support, Instruction Trace

- V 强大的 操作系统支持

- ❷用户/管理模式

- Ø操作系统支持特性

- V 可以完全的使用C语言来编程

- ❷甚至是复位,中断和异常

# 华清远见

## 与其它的ARM处理器的区别

- ∨ ARMv7M 体系结构

- V 没有ARM指令集的支持

- Ø 仅仅只有Thumb-2指令集

- ∨ 没有高速缓冲存储器 (Cache), 没有存储器管理单元(MMU)

- ∨ 调试使微控制器应用最优化

- ∨ 向量表存放的是地址而不是指令

- ✓ 中断自动的保存/恢复程序状态

- V 异常处理程序可以用C语言来编写

- ∨ 没有协处理器cpl5

- Ø 所有的寄存器是存储器映射的

- ∨ 中断控制器是Cortex-M3内核的一部分

## ARM Cortex-M3 规范

- § ARM v7M接口体系结构

- § Thumb-2指令体系结构

- ₹ 硬件除法器&单周期乘法

- Ü 对运算加速

- § 完整的可嵌套的向量中断控制器(NVIC)

- **ü** 32个物理中断/8种优先级(硬件)

- **Ü** 可配置的1-244个物理中断

- **Ü** 可设置达到256个优先级一通过硬件和软件配置

- § Integrated Bus Matrix

- **ü** Bus Arbiter

- **ü** Bit Banding Atomic Bit Manipulation

- **Ü** Write Buffer

- **Ü** Memory (I&D) plus System Interface & Private Peripheral Bus

- ∨Cortex-M3发展及应用

- ∨Cortex-M3内核体系结构

- ∨Thumb-2指令集

- ∨Cortex-M3接口设计

- VCortex-M3与操作系统

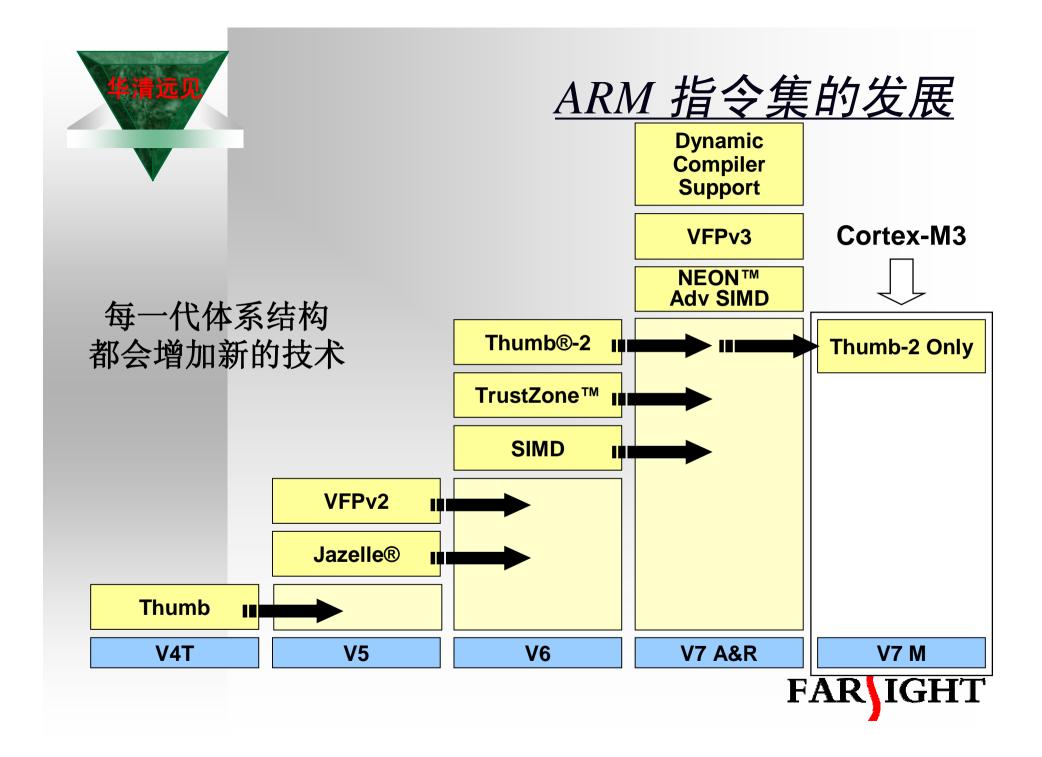

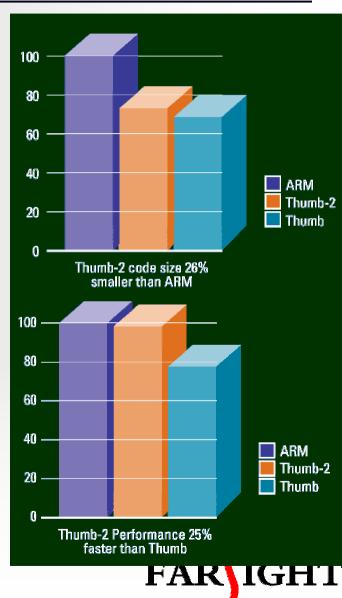

- v Variable-length instructions

- ARM instructions are a fixed length of 32 bits

- Thumb instructions are a fixed length of 16 bits

- Thumb-2 instructions can be either 16-bit or 32-bit

- Code size benefits

- Thumb-2 gives approximately 26% improvement in code density over ARM

- Performance benefits

- Thumb-2 gives approximately 25% improvement in performance over Thumb

- ▼ The Cortex-M3 implements ONLY the Thumb-2 instruction set

## 指令分类

- **∨** Data processing Instructions

- **V** Branch and Control Flow Instructions

- **∨** Memory Access Instructions

- **v** Exception Generating Instructions

- **∨** Accessing Special Registers

- **v** Coprocessor Instructions

- **∨** Memory Barriers and Synchronization

- ∨Cortex-M3发展及应用

- ∨Cortex-M3内核体系结构

- ∨Thumb2指令集

- ∨Cortex-M3接口设计

- VCortex-M3与操作系统

## 接口设计的关注点

- V对任何一块新的芯片, 关注

- **Ø** Memory map

- **Ø** Interrupt

# 华清远见

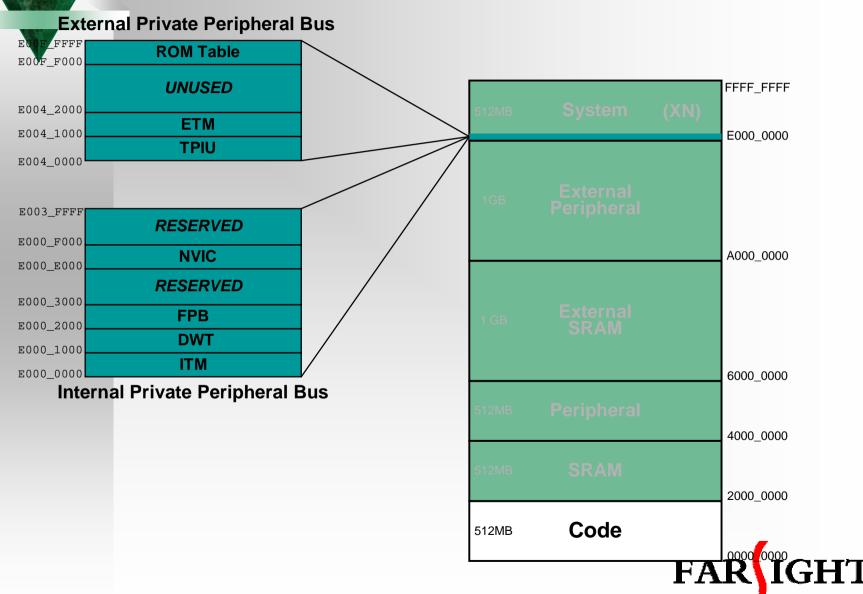

### Cortex-M3 Memory Map

### Cortex-M3 Fixed Memory Map

✓ All peripheral registers are memory-mapped

Ø Includes Interrupt registers and debug registers

- ▼ Fixed region for internal instruction store

- **Ø** Up to 512 MB

- Normally this is Flash Memory

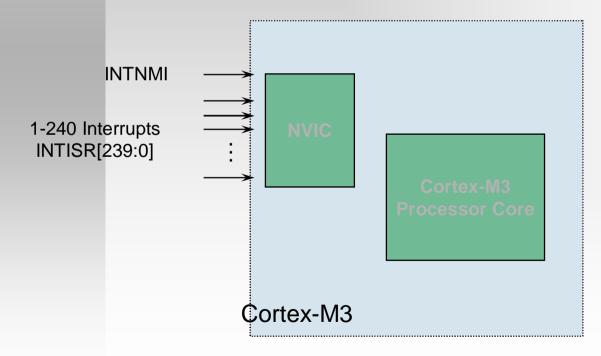

## Cortex-M3 Interrupts

- One Non-Maskable Interrupt (INTNMI) supported

- 1-240 prioritizable, maskable interrupts supported

Implementation option selects number of interrupts supported

- ▼ Interrupt Controller (NVIC) is tightly coupled with processor core

- ▼ Interrupt inputs are active HIGH

## <u>中断处理</u>

- Exceptions/interrupts processed in Handler mode

- Supervisor privilege

- ✓ Interruptible LDM/STM for low interrupt latency

- **Ø** Continued on return from interrupt

- Automatic save and restore of processor state

- Ø {PC, xPSR, R0-R3, R12, R14}

- Provides low latency interrupt/exception entry and exit

- Allows handler to be written entirely in 'C'

### <u>NVIC</u>

NVIC gives low latency interrupt processing

✓ Option to synthesize between 1 & 240 interrupt channels

▼ Interrupt entry address passed directly to core

- ∨Cortex-M3发展及应用

- ∨Cortex-M3内核体系结构

- ∨Thumb2指令集

- ∨Cortex-M3接口设计

- ∨Cortex-M3与操作系统

# 嵌入式操作系统的发展

应用程序

应用程序

通信协议

库函数

应用程序

操作系统内核

文件系统

API GUI

文件系统

API GUI

操作系统内核

驱动程序和固件

驱动程序和固件

操作系统内核

驱动程序和固件

80年代初期

80年代中期-90年代中 期

90年代末期-21世纪

# 常见的嵌入式操作系统

- ı Ucos

- ThreadX

- ı Vxwork

- ı Nucleus

- · WindowsCE

- ı Li nux

## 学习嵌入式操作系统

- ∨ 学习一种实时操作系统RTOS, 如μC/OS- II, 掌握实时系统的概念和设计方法

- ✓ 嵌入式系统以应用为中心,要选择"适用"的操作系统

- ∨ 嵌入式Li nux

- ∨ 自己尝试"写"RTOS

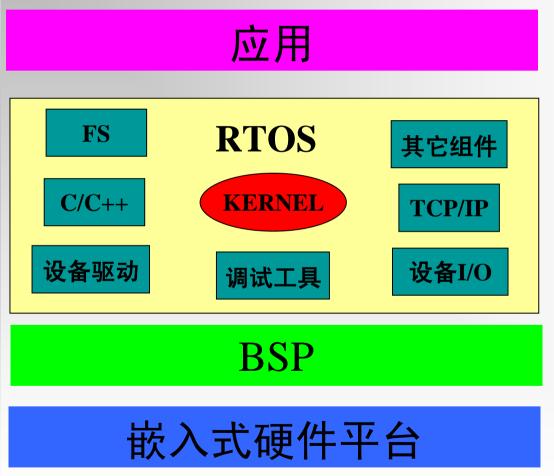

## RTOS在嵌入式系统中的位置

# mC/OS简介

- 1、μC/OS——Mi cro Controller 0 S,微控制器操作系统

- 2、 μC/OS简介

- Ø 美国人Jean Labrosse 1992年完成

- ☑ 应用面覆盖了诸多领域,如照相机、医疗器械、音响设备、发动机控制、高速公路电话系统、自动提款机等

- Ø 1998年μC/0S-II, 目前的版本μC/0S-II V2.61, 2.72

- Ø 2000年,得到美国航空管理局(FAA)的认证,可以用于飞行器中

- Ø 网站www.ucos-II.com (www.micrium.com)

## mC/OS的性能特点

#### ☑ 公开源代码

#### u 可移植性(Portable)

绝大部分μ C/OS-II的源码是用移植性很强的ANSI C写的。和微处理器硬件相关的那部分是用汇编语言写的。汇编语言写的部分已经压到最低限度,使得μ C/OS-II 便于移植到其他微处理器上。 μ C/OS-II 可以在绝大多数8位、16位、32位以至64位微处理器、微控制器 、数字信号处理器 (DSP) 上运行。

#### u 可固化 (ROMable)

μ C/OS-II是为嵌入式应用而设计的,这就意味着,只要用户有固化手段(C编译、连接、下载和固化), μ C/OS-II可以嵌入到用户的产品中成为产品的一部分。

#### u 可裁剪 (Scalable)

可以只使用μ C/OS-II中应用程序需要的那些系统服务。也就是说某产品可以只使用很少几个μ C/OS-II调用,而另一个产品则使用了几乎所有μ C/OS-II的功能,这样可以减少产品中的μ C/OS-II所需的存储器空间(RAM和ROM)。这种可剪裁性是靠条件编译实现的。

### 华清远见 - Cortex M3及Ucos

周末班: 共4天, 每天6学时, 总计24学时

## Cortex M3及Ucos

- ü 了解Cortex-M3体系结构及thumb-2指令集,并掌握在Cortex-M3体系结构上进行嵌入式编程的方法;

- 道 掌握STM32F103处理器各个接口开发的原理;

- Ü嵌入式操作系统的基本概念及实际工程应用。

- ü 了解uC/OS-II操作系统工作原理,掌握uC/OS-II 操作系统移植方法;

- ü 掌握在uC/OS-II操作系统上的编程方法及编程技巧。

#### 华清远见 - ARM开发培训班

周末班: 5天,每天6学时, 总计30学时

## ARM开发培训班

- ü ARM体系结构

- ü ARM编程模型

- ü ARM异常处理

- ü ARM、THUMB指令集

- ü C、C++、汇编混合编程

- Ü 高效的嵌入式软件设计技巧

- Ü 常用外围设备接口开发及试验

- ü Bootloader开发以及Linux系统的引导

The success's road

www.farsight.com.cn

谢谢!